synchronous MOSFETs in a 16-pin QSOP package. With very few external components, a 2A step-down DC:DC converter can be very easily built, resulting in saved board space (0.5in<sup>2</sup>), minimal design effort, and improved design time.

consideration and lists the bill of materials and the layout. Please also refer to the advanced data sheet of EL7562 for detailed applications of the features.

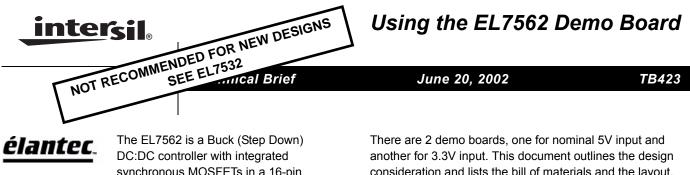

## EL7562 Demo Board Circuit Schematic for V<sub>IN</sub> = 5V Application

#### EL7562 Demo Board Bill of Material V<sub>IN</sub> = 5V, V<sub>OUT</sub> = 3.3V

| REFERENCE<br>DESIGNATION | VALUE           | MANUFACTURER | MANUFACTURER'S<br>PHONE NUMBER | PART NUMBER    |

|--------------------------|-----------------|--------------|--------------------------------|----------------|

| C1                       | 100µF           | Sprague      | 207-324-4140                   | 293D107X0010D2 |

| C2, C3, C5, C6           | 0.1µF, 0603     | Any          |                                |                |

| C4                       | 270pF, 5%, 0603 | Any          |                                |                |

| C7                       | 100µF           | Sprague      | 207-324-4140                   | 293D107X0010D2 |

| L1                       | 4.7µH           | Coilcraft    | 847-639-6400                   | D01813472HC    |

| R1                       | 1kΩ, 0603       | Any          |                                |                |

| R2                       | 2370Ω, 0603     | Any          |                                |                |

| R3                       | 39Ω, 0603       | Any          |                                |                |

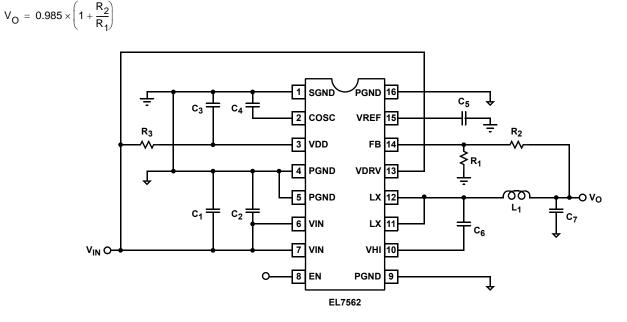

EL7562 Demo Board Circuit Schematic for  $V_{IN}$  = 3.3V Application

## **EL7562 Demo Board Bill of Material** $V_{IN}$ = 3.3V, $V_{OUT}$ = 2.5V

| REFERENCE<br>DESIGNATION | VALUE            | MANUFACTURER      | MANUFACTURER'S<br>PHONE NUMBER | PART NUMBER    |

|--------------------------|------------------|-------------------|--------------------------------|----------------|

| C1                       | 100µF            | Sprague           | 207-324-4140                   | 293D107X0010D2 |

| C2, C3, C5, C6, C8, C9   | 0.1µF, 0603      | Any               |                                |                |

| C4                       | 270pF, 5%, 0603  | Any               |                                |                |

| C7                       | 100µF            | Sprague           | 207-324-4140                   | 293D107X0010D2 |

| L1                       | 4.7µH            | Coilcraft         | 847-639-6400                   | D01813472HC    |

| R1                       | 1kΩ, 0603        | Any               |                                |                |

| R2                       | 1.54kΩ, 0603     | Any               |                                |                |

| R3                       | <b>39Ω, 0603</b> | Any               |                                |                |

| D2, D3/4                 | Bat54S           | Vishay Telefunken | 402-563-6863                   | Bat54S         |

### **Design Considerations**

#### **Choosing the Component Values**

The following requirements are specified for a DC:DC converter:

- Input voltage range: V<sub>IN</sub> = 4.5V-5.5V

- Output voltage: V<sub>O</sub> = 3.3V

- Max output voltage ripple: ∆V<sub>O</sub> = 50mV

- Output max current: I<sub>O</sub> = 2A

The following steps briefly outline the steps to choose components.

1. Choose the feedback resister divider.

The output voltage is decided by:

$$V_{OUT} = 0.985 \times \left(1 + \frac{R_2}{R_1}\right)$$

For V<sub>IN</sub> = 5V

$$V_{OUT} = 0.975 \times \left(1 + \frac{R_2}{R_1}\right)$$

For V<sub>IN</sub> = 3.3V

2. Choose the converter switching frequency  $F_S$ .

$F_S$ , inductor L<sub>1</sub>, output capacitor C<sub>7</sub>, and EL7562's switching loss are closely related. many iterations (or thermal measurements) may be required before a final value can be decided.

Please refer to the EL7562 data sheet for the  ${\sf F}_S$  vs  ${\sf C}_{OSC}$  curve.

3. Inductor L<sub>1</sub>.

The EL7562 is internally ramp-compensated. For optimal operation, the inductor current ripple should be less than 0.6A.

If  $\Delta I_L$  = 0.5A, then:

$$L = \frac{(1 - D) \times V_{O}}{\Delta I_{L} \times F_{S}}$$

where:

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}}}{\mathsf{V}_{\mathsf{IN}}}$$

Choosing L<sub>1</sub> = 4.7 $\mu$ H yields  $\Delta$ I<sub>LMAX</sub> = 0.56A. L<sub>1</sub> should also be able to handle DC current of 2A and peak current of 2.3A at temperature range.

4. Output capacitor C7.

$\Delta V_O$  and  $\Delta I_L$  normally decide  $C_7$  value.  $\Delta V_O$  requires ESR of  $C_7$  be less than:

$$\mathsf{ESR} = \frac{\Delta \mathsf{V}_{\mathsf{O}}}{\Delta \mathsf{I}_{\mathsf{LMAX}}} = 89 \mathsf{m}\Omega$$

Double-check the RMS current requirement of the output capacitor:

$$\Delta I_{C7} = \frac{\Delta I_{LMAX}}{\sqrt{12}}$$

which is 0.16A. For a capacitor or combination of capacitors with  $89m\Omega$  parallel ESR, it is more than enough to handle this current.

5. Input capacitors  $C_1$  and  $C_2$ .

If all the AC current is handled by the input capacitors its RMS current is calculated as:

$$I_{IN,rms} = \sqrt{[D \times (1 - D)]} \times I_{O}$$

This gives almost 0.99A when D =  $D_{MAX}$ . Therefore a cap with 0.99A current handling capability should be chosen. However, in case some other capacitor is sharing current with it, this current requirement can be reduced.

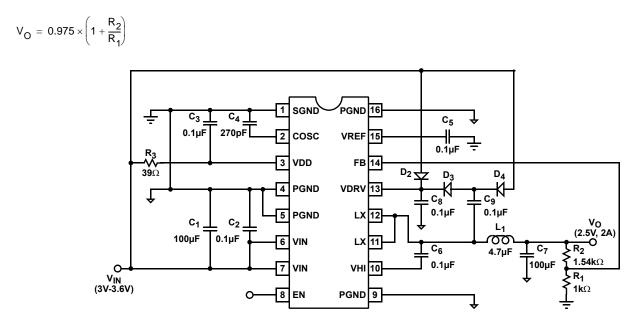

#### Layout Considerations

The layout is very important for the converter to function properly. Power Ground  $(\downarrow)$  and Signal Ground  $(\downarrow)$  should be separated to ensure that the high pulse current in the Power Ground never interferes with the sensitive signals connected to Signal Ground. They should only be connected at one point (normally at the negative side of either the input or output capacitor.)

The trace connected to pin 14 (FB) is the most sensitive trace. It needs to be as short as possible and in a "quiet" place, preferably between the PGND and SGND traces.

In addition, the bypass capacitor  $C_3$  should be as close to pins 1 and 3 as possible.

The heat of the chip is mainly dissipated through the PGND pins. Maximizing the copper area around these pins is preferable. In addition, a solid ground plane is always helpful for the EMI performance.

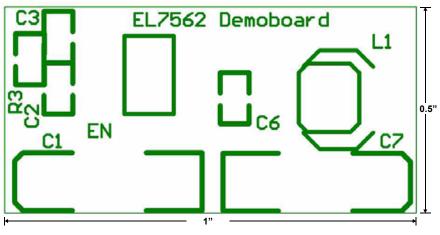

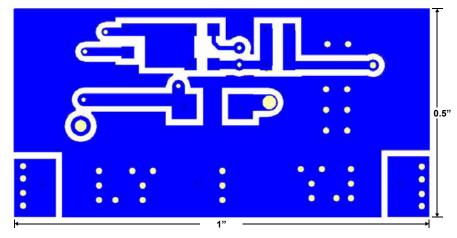

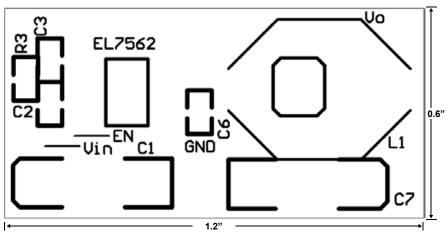

## Demo Board Layout for $V_{IN} = 5V$

FIGURE 1. TOP LAYER

FIGURE 2. TOP SILKSCREEN

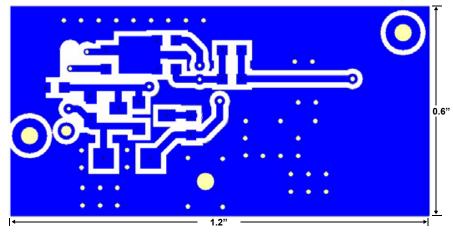

Demo Board Layout for V<sub>IN</sub> = 5V (Continued)

FIGURE 3. BOTTOM LAYER

FIGURE 4. BOTTOM SILKSCREEN

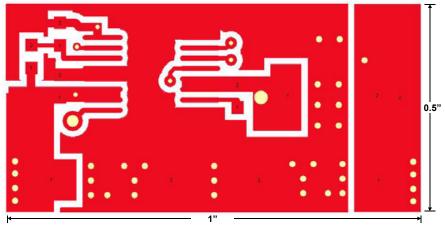

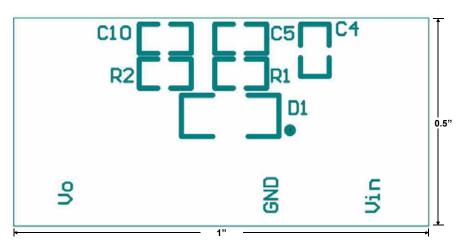

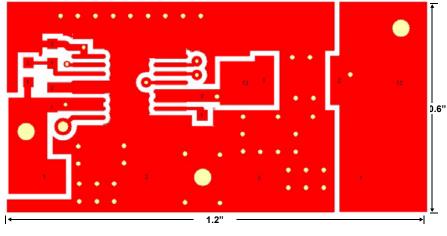

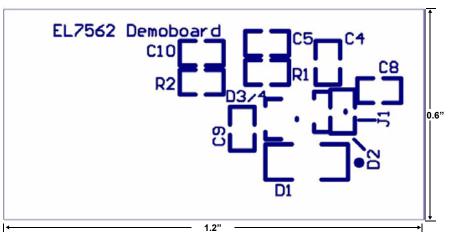

# Demo Board Layout for $V_{IN} = 3.3V$

FIGURE 5. TOP LAYER

FIGURE 6. TOP SILKSCREEN

Demo Board Layout for V<sub>IN</sub> = 3.3V (Continued)

FIGURE 7. BOTTOM LAYER

FIGURE 8. BOTTOM SILKSCREEN

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com